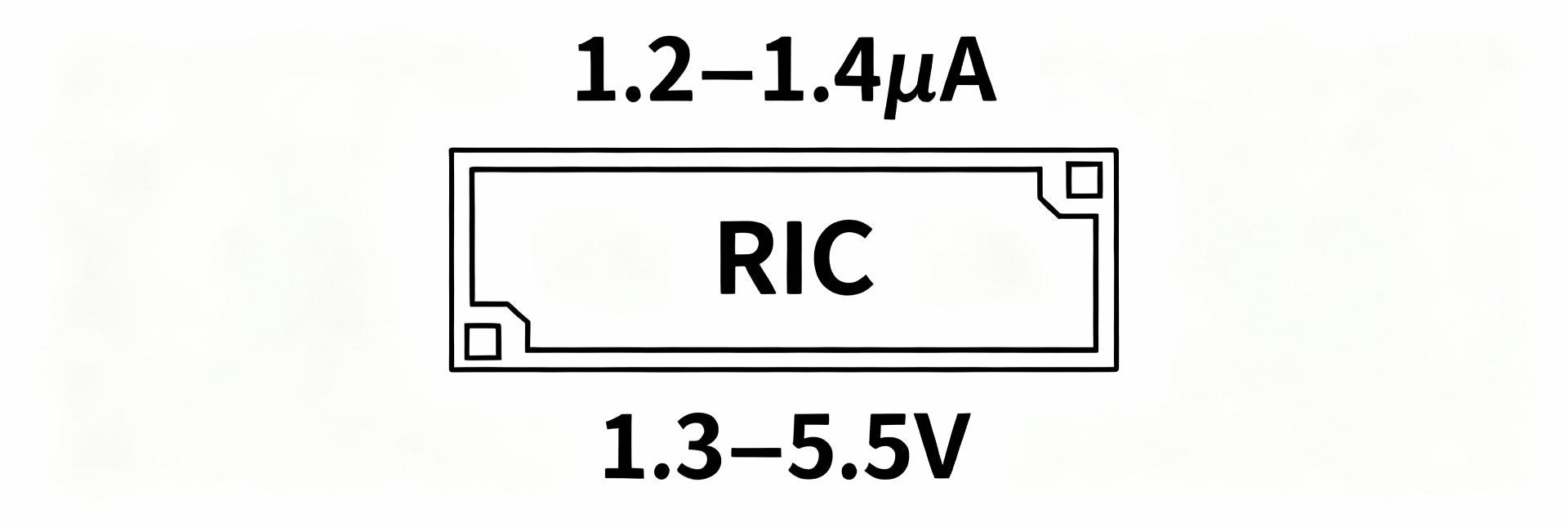

The S-35190AH-T8T2U specifies timekeeping current of 1.2–1.4 μA (at 3–5 V), a measurable indicator of its low-power profile for battery-backed RTC designs. This report summarizes the device's key electrical specs, measured/test-relevant metrics, practical integration guidance, comparative benchmarking templates, and a pre-production deployment checklist. Readers will find action-oriented advice for schematic/layout, power sequencing, firmware considerations, and validation tests suitable for embedded and automotive-grade applications.

Background: Product Family & Use Cases

S-35190A H Series overview

Point: The S-35190A H Series is positioned as a 3-wire RTC IC family targeting automotive and industrial systems. Evidence: ABLIC's product documentation describes the family as automotive-grade real-time clock devices available in 8-TSSOP packages. Explanation: The 3-wire interface simplifies host connections compared with I2C, reducing pin count for microcontroller-based telematics, data loggers, and low-power consumer products. Typical variants differ in temperature ratings and pin features; designers choose the H-series when robust voltage range and automotive-quality validation are required.

Operating envelope & certification highlights

Point: The family supports a wide operating envelope essential for embedded harsh environments. Evidence: Key parameters include operating temperature from −40°C to +105°C and a supply/battery voltage range spanning 1.3–5.5 V, with RoHS and automotive suitability called out by the manufacturer. Explanation: Wide temperature and voltage ranges reduce failure risk in automotive under-hood or industrial deployments; the wide battery-voltage tolerance enables use with common coin cells and supercaps. Certification notes inform procurement and qualification planning for safety-critical systems.

Primary use-case scenarios

Point: The S-35190A H Series fits several primary scenarios and has constraints. Evidence: Recommended use-cases include battery-backed clocks, data loggers, and telematics nodes; constraints include designs requiring sub-μA hold currents or integrated supercapacitor management. Explanation: For battery-backed timekeeping where multi-year retention on a CR2032 is a goal, the specified timekeeping current is advantageous. Conversely, systems requiring integrated tamper-proof features or extreme ultra-low standby currents might favor alternative parts or add external power-management circuitry.

S-35190AH-T8T2U Key Specs Overview

Timekeeping & calendar features

Point: The device implements standard RTC time and calendar formats with alarms and leap-year handling. Evidence: Supported formats include HH:MM:SS (12/24-hour), date as YY-MM-DD-dd, leap-year logic, and multiple alarm functions. Explanation: Firmware must account for 12/24-hour rollovers, two-digit-year handling, and alarm interrupt masks; robust driver design should include validation for leap-year transitions and DST adjustments if required. Alarm debounce and low-power wake sequencing should be included in system design.

Electrical specifications (quick reference)

Point: Critical electrical specs determine system-level power budgets. Evidence: Supply voltage: 1.3–5.5 V; timekeeping current: 1.2–1.4 μA @ 3–5 V; backup-battery range supports typical coin cells and supercaps; I/O drive suited for standard MCU GPIO. Explanation: The low timekeeping current directly affects battery retention estimates. I/O drive and logic thresholds influence level-shifting choices; designers should capture these numbers in a single-line reference to speed evaluation.

| Parameter | Value / Notes |

|---|---|

| Supply voltage | 1.3–5.5 V |

| Timekeeping current | 1.2–1.4 μA @ 3–5 V |

| Package | 8-TSSOP (SMD) |

Package, pinout & physical constraints

Point: Mechanical and thermal characteristics inform PCB and thermal design. Evidence: The S-35190AH-T8T2U uses an 8-TSSOP SMD package with compact footprint and standard pin spacing; thermal derating applies at high ambient. Explanation: For high-temperature or constrained airflow environments, designers should verify solder-pad and thermal relief strategies; the small package eases board area but requires careful thermal vias and solder fillet control to maintain reliability across −40°C to +105°C.

Electrical Performance Deep-Dive (measurements & implications)

Timekeeping current: measurement conditions & impact

Point: Timekeeping current must be measured under controlled voltages and temperatures to be meaningful for battery-life planning. Evidence: The specified 1.2–1.4 μA figure is given for 3–5 V in manufacturer test conditions; in-circuit measurements differ due to pull-ups, leakage, and measurement probe loading. Explanation: To estimate battery life, measure the device in its final board state with all pull-ups and passive leakage present, record current at multiple temperatures, and use standard capacity fade models to estimate years of retention. Minimizing standby current requires removing unnecessary pull-ups, using high-impedance GPIOs, and isolating peripheral leakage paths.

Supply range behavior & power-fail scenarios

Point: Behavior across the 1.3–5.5 V supply range includes automatic backup switching and brown-out handling. Evidence: The RTC shifts to backup-battery operation when VDD falls below its internal detection threshold; recommended decoupling and layout practices appear in manufacturer notes. Explanation: Designers should provide a robust VDD monitoring strategy, place decoupling capacitors close to VDD pins, and use a diode-OR or ideal diode arrangement for backup switching. Layout should minimize ground bounce and ensure the backup battery path remains contiguous during connector events.

Accuracy, clock correction & temperature effects

Point: Clock accuracy is subject to oscillator characteristics and temperature drift; correction features mitigate long-term drift. Evidence: Datasheet lists ppm drift ranges and any built-in correction registers or calibration steps. Explanation: Strategy options include periodic NTP/or host synchronization, temperature-table compensation in firmware, or optional external TCXOs if sub-ppm accuracy is required. Logging measured drift across the operational temperature range enables an empirically derived correction table to run in production firmware.

Integration & Design Guide (practical how-to)

Schematic & PCB layout best practices

Point: PCB layout and schematic choices affect standby current, EMC, and thermal performance. Evidence: Best practices include placing decoupling capacitors adjacent to VDD, keeping the backup-battery trace short, and isolating noisy power planes. Explanation: Place the backup coin cell near the RTC to reduce leakage paths, separate high-frequency switching nets from the 3-wire interface, and avoid routing noisy clocks adjacent to RTC traces. Thermal relief on TSSOP pads prevents solder fatigue; ensure consistent stencil design for reliable joints through thermal cycles.

SPI-like 3-wire interface: timing and driver notes

Point: The 3-wire signaling (clock, data, latch) requires defined timing margins and compatible drive strengths. Evidence: Interface timing parameters include setup/hold times and allowable clock rate ranges; recommended host GPIO drive strengths are moderate to avoid ringing. Explanation: Use host-driven assertions: drive clock with a controlled slew rate, sample data on the specified edge, and respect minimum idle times. Example pseudocode: assert CS, for each bit toggle CLK, sample DATA, deassert CS; implement retries on CRC/ACK errors and use pull resistors sized to minimize quiescent current.

Power sequencing, backup battery selection & testing

Point: Selecting the backup chemistry and testing power transitions is critical to retention and safety. Evidence: Recommended backup options include coin cell (e.g., CR2032 equivalent) or small Li-based backup with proper protection; supercapacitors are an alternative where high cycle life is needed. Explanation: For long retention, CR2032 offers multi-year life at μA currents; supercaps provide high-cycle, short-term retention suitable for store-and-forward scenarios. Test scenarios should include rapid VDD loss, gradual brown-out, and repeated power cycling to validate data retention and the host's recovery logic.

Comparative Case Studies & Benchmarks

Benchmarked metrics vs. similar RTC ICs

Point: Benchmark templates focus on the most impactful metrics for selection. Evidence: Typical comparison metrics include timekeeping current, supply range, temp rating, alarm features, and package. Explanation: Use a standardized table to capture these numbers across candidate parts so tradeoffs become explicit; include measured in-circuit currents rather than datasheet minima for realistic comparison.

| Metric | S-35190AH-T8T2U | Competitor A | Competitor B |

|---|---|---|---|

| Timekeeping current | 1.2–1.4 μA (3–5 V) | — | — |

| Supply range | 1.3–5.5 V | — | — |

| Temp rating | −40°C to +105°C | — | — |

Two short integration case studies

Point: Practical case studies illustrate tradeoffs in real designs. Evidence: Case A — a low-power data logger used the device with a CR2032 and aggressive host sleep strategy; runtime increased by years compared to a 5 μA RTC. Case B — an automotive telematics node prioritized temp rating and brown-out resilience. Explanation: In Case A, measured quiescent budget and occasional sync windows preserved multi-year retention; in Case B, board-level thermal routing and robust backup switching maintained time across vehicle power transients.

Failure modes & troubleshooting checklist

Point: Common failure modes can be diagnosed with a structured checklist. Evidence: Typical issues include time drift, interface errors, and backup loss. Explanation: Debug flow: 1) Verify VDD and backup-battery voltages with high-resolution meter; 2) Scope the 3-wire interface for correct levels and timing; 3) Read and validate configuration registers; 4) Reproduce under temperature to isolate thermal-related drift. Document each step and include regression tests in QA.

Evaluation & Deployment Checklist (actionable next steps)

Pre-production validation plan

Point: A formal lab plan reduces late-stage surprises. Evidence: Required tests include timekeeping current across temperature, backup retention, interface stress, ESD, and thermal cycling. Explanation: Define pass/fail criteria up front (e.g.,

Firmware & QA tests to include

Point: Firmware tests should exercise edge cases and long-run behaviors. Evidence: Include RTC read/write integrity, leap-year and alarm edge cases, power-fail recovery, and long-term drift tracking. Explanation: Automate nightly drift logs, exercise alarm wake paths under low-power host states, and run randomized power-cycling to validate non-volatile state and register consistency. These tests detect timing bugs that only appear after many cycles.

Procurement, compliance & sourcing notes

Point: Sourcing and compliance steps reduce supply and compliance risk. Evidence: Evaluate reel/packaging options, lead-time variability, and counterfeit prevention steps; reference the manufacturer’s datasheet revision. Explanation: Prioritize authorized distributors, request traceability certificates for automotive programs, and pin the exact datasheet version in the BOM. Factor lead times into NPI schedules and ensure alternate sourcing paths if production volumes scale.

Summary

The S-35190AH-T8T2U combines wide supply range, −40°C to +105°C operation and very low timekeeping current (1.2–1.4 μA), making it a practical RTC IC for battery-backed and automotive applications. Next step: run the pre-production validation checklist, measure in-circuit timekeeping current across target temperatures, and compare results against target specs to confirm fit for purpose.

- The S-35190AH-T8T2U delivers low standby current and wide supply tolerance, enabling long battery retention in embedded designs.

- Designers should prioritize decoupling, short battery traces, and minimal pull-ups to preserve the low timekeeping current.

- Validation must include temperature sweep of timekeeping current, power-fail transitions, and long-term drift logging to finalize firmware correction tables.

Frequently Asked Questions

How should the S-35190AH-T8T2U timekeeping current be measured in-circuit?

Measure timekeeping current with the device in its final board state and all peripherals disconnected or tri-stated to avoid external leakage. Use a low-current, high-resolution meter in series with the backup path or VDD as appropriate, and record values at multiple temperatures (e.g., −40°C, 25°C, +85°C). Subtract known board leakage by measuring a populated test board with the RTC removed or mocked; document measurement methodology for reproducibility.

What backup battery types are recommended when using this RTC IC?

Common choices include coin cells (e.g., CR2032 equivalents) for multi-year retention at μA currents, or small supercapacitors for short-term high-cycle requirements. Selection depends on expected retention time, temperature range, and safety considerations. For automotive-grade deployments, ensure the chosen chemistry meets temperature and vibration requirements and include overvoltage/short protection as part of the backup circuit design.

Which firmware tests are most important to validate RTC integration?

Prioritize read/write integrity under concurrency and power transitions, leap-year and end-of-month rollovers, alarm wake and debounce behavior, and long-term drift tracking with periodic synchronization. Include randomized power-cycle tests and stress tests that toggle the 3-wire interface timing to reveal edge-case failures. Automating these tests speeds regression and provides traceable evidence for production acceptance.